On Synchronization Primitive Systems

Бу

Richard J. Lipton

Research Report #22

This work is a slightly different version of the author's doctoral dissertation, prepared for the Computer Science Department at Carnegie-Mellon University, 1973. A portion of this work was supported by the Sloan Foundation.

October 1973

#### ABSTRACT

We study the question: what "synchronization primitive" should be used to handle inter-process communication? We present a formal model of the process concept, and then we use this model to compare four different synchronization primitives. We are able to prove that there are differences between these synchronization primitives. Although we compare only four synchronization primitives, our general methods can be used to compare other synchronization primitives. Moreover, in our definitions of these synchronization primitives, we explicitly allow conditional branches. In addition, our model separates the notion of scheduler; this separation allows us to unravel the controversy between Brinch Hansen and Courtois, Heymans, Parnas and to define formally the release mechanism of the PV synchronization primitive.

# 1. INTRODUCTION

Dijkstra [1968a] has demonstrated how an operating system can be designed and validated by using a "synchronization primitive" to handle inter-process communication. Since this accomplishment, an important issue in the design of an operating system has been:

(\*) What "synchronization primitives" should be used to handle inter-process communication?

Dijkstra used the "synchronization primitive" PV; however, other synchronization primitives have been proposed. Currently, the selection of a synchronization primitive is an ad hoc design decision.

The current attempts to answer the question (\*) each show that a given synchronization primitive can "solve" a given "synchronization problem".

These synchronization problems include the "mutual exclusion problem" (Dijkstra [1968]), the "first and second reader-writer problems" (Courtois, Heymans, Parnas [1971], Brinch Hansen [1972, 1972a]), and several buffer problems

(Habermann [1972], Dijkstra [1972]). The basic assumption of their research is that the capabilities of a synchronization primitive can be determined by trying to solve problems that are found in operating systems. One of the dangers of this approach is that our inability to "solve" a problem can stem from two causes: either our inability to find a solution or the non-existence of a solution. In fact, several people have asserted that the "first reader-writer problem" was not "solvable" by PV; Courtois, Heymans, Parnas [1971] have shown that this "synchronization problem" is

"solvable" by PV. Another danger of this approach is that we can never

be certain that each researcher is using the same notions of "solve" and

"synchronization problem". The controversy between Courtois, Heymans, Parnas

and Brinch Hansen over the "second reader-writer problem" can be attributed

to the informal nature of their research. (Courtois, Heymans, Parnas

[1972], Parnas [private communication], Brinch Hansen [1973]).

We study the question (\*) from a formal viewpoint. We will present a formal model of the process concept, and then use this model to compare several different synchronization primitives. We are able to prove that there are differences between several synchronization primitives. Some of these differences have - on a very informal level - been noticed before, i.e., Wodon [1972] and Parnas [private communication]. In addition, our model of the process concept separates the . notion of process from the notion of scheduler, this separation allows us to unravel the controversy between Brinch Hansen and Courtois, Heymans, Parnas and to state formally the theorem in Habermann [1972].

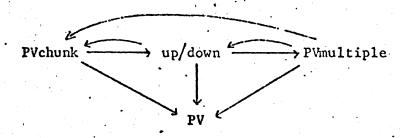

We study four synchronization primitives: PV, which is due to Dijkstra [1968, 1968a]; PVchunk, a generalization of PV due to Vantilborgh and van Lamsweerde [1972]; PV multiple, a generalization PV due to Patil [1971] and Dijkstra [unpublished]; and up/down, a generalization of PV due to Wodon [1972]. Although we compare only these synchronization primitives, our general methods can be used to compare other synchronization primitives such as block/wakeup (Saltzer [1966]). In our definitions of these synchronization primitives we explicitly allow conditional branches. Therefore, our results are not

related to the results of Patil [1971], nor are they related to the results of Parnas [1972].

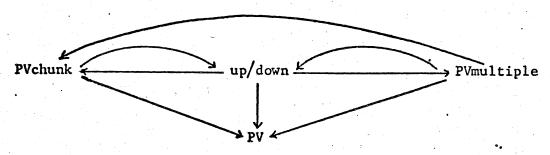

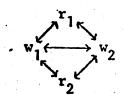

We define a relation " $\rightarrow$ " between synchronization primitives. Informally,  $x \rightarrow y$  means that the synchronization primitive y cannot "solve some synchronization problem" that x can. Our principal results are displayed in Figure 1, where an arrow from x to y means that  $x \rightarrow y$ .

FIGURE 1.

Each of the arrows in Figure 1 can be traced to a particular synchronization problem.

1. up/down PVchunk, up/down PVmultiple, up/down PV. These relations are true because up/down can solve the second reader-writer problem while PVchunk, PVmultiple, and PV cannot. These results do not contradict the "solutions" found in Courtois, Heymans, Parnas [1971] and in Brinch Hansen [1972,1972a]; the notions of solve used by these researchers are weaker than the notion used here. One of our contributions is that we can define several notions of "solve" - all in a precise way.

- 2. PVmultiple → PVchunk, PVmultiple → PV. These relations are true because PVmultiple can solve the "Five Dining Philosophers" (Dijkstra [1971]) while PVchunk and PV cannot. As in (1) these results do not contradict the "solution" presented by Dijkstra.

- 3. PVmultiple up/down, PVchunk up/down, PVchunk PV. These relations are true because PVmultiple and PVchunk can "solve" the "first reader-writer problem with a bound on the number of readers that can be reading at one time" while up/down and PV cannot. This is a new "synchronization problem". Although, we can trace these results to particular synchronization problems they are indicative of general phenomena.

This paper is organized into eight sections. In section 2 our model of the process concept is defined. The main result of this section is that processes that use synchronization primitives for interprocess communication satisfy four basic properties: these properties are not dependent on which synchronization primitive the process uses. In section 3 the concept of scheduler is defined. We use the notion of scheduler to state the theorem of Habermann [1972]. In section 4 we define several relations between processes. In defining these relations we formalize the concept of a "synchronization problem". In section 5 and 6 a structure theorem is stated and proved — using just the four basic properties of section 2 — that reduces the question

is  $x \rightarrow y$ ?

to a combinatorial question. In section 7 we use this reduction to compare the synchronization primitives PV, PVchunk, PVmultiple, and

up/down. In particular, the results displayed in Figure 1 are proved in this section. In section 8 a summary and a list of open problems are presented.

#### 2. PROCESSES

We now define a general model of the process concept;

later on we add additional structure to this model. The resulting model - a C process - is then studied in detail, and several basic properties of C processes are proved.

## 2.1 A GENERAL MODEL OF PROCESSES

1. <u>Definition</u>.  $P = \langle A, \emptyset, w \rangle$  is a <u>process</u> if A is a set of functions from  $\emptyset$  to  $\emptyset$  and w is in  $\emptyset$ . The elements of A are the <u>actions</u> of the process P.

The set  $\emptyset$  is the <u>data structure</u> of the process; the element w is the <u>initial data structure</u> element of the process. We will use P and Q to denote processes, and we will use P, Q, Q to denote processes, and we will use Q, Q, to denote actions.

Actions - as defined in Definition 1 - are arbitrary functions from  $\mathfrak{I}$  to  $\mathfrak{I}$ . The data structure of a process - as defined in Definition 1 - is an arbitrary set. Later we will place additional restrictions on both the actions and the data structure. Note, P will usually be a "parallel process", i.e., our concept of a process is what is usually called a set of "sequential processes".

#### 2.2 NOTATION

We will now introduce a shorthand for describing actions. The notion is just a method of describing functions in a convenient and readable way. The theory is unchanged if we change notation. Let N be

a set, and let  $(x_1,...,x_k)$  be a typical element of  $\mathfrak{J}$ . The notation

when

$$B(x_1,...,x_k) \stackrel{\text{do}}{=} x_1 \leftarrow f_1(x_1,...,x_k);...;x_k \leftarrow f_k(x_1,...,x_k)$$

where B is a predicate and each  $f_i$  (i=1,...,k) is a function, denotes the function g, from  $\mathfrak{J}$  to  $\mathfrak{J}$ , defined by

(1) if

$$B(y_1,...,y_k)$$

is true, then  $g(y_1,...,y_k) = (f_1(y_1,...,y_k),...,f_k(y_1,...,y_k))$

(2) if

$$B(y_1,...,y_k)$$

is false, then  $g(y_1,...,y_k) = (y_1,...,y_k)$ .

Caution, we consider that the assignments after the 'do' are all done "simultaneously" and not "sequentially". For example, suppose that '(A,B)' is a typical element of the set  $\{1,2,3\} \times \{1,2,3\}$ , and that  $f = when A < B do A \leftarrow 1$ ;  $B \leftarrow A$ . Then f(2,3) is equal to (1,2). We will delete assignments of the form 'x  $\leftarrow$  x'. For instance, we will shorten when L = 0 do  $L \leftarrow 1$ ;  $B \leftarrow B$ ;  $C \leftarrow C$  to when L = 0 do  $L \leftarrow 1$ .

We use small Greek letters to denote <u>finite</u> or <u>infinite</u> sequences; the empty or null sequence will be denoted by A.

If  $\alpha$  is a finite sequence and  $\beta$  is a finite or infinite sequence, then the sequence formed by concatenating  $\alpha$  and  $\beta$  is denoted by  $\alpha\beta$ . Define  $\alpha \leq \beta$  if for some  $\delta$ ,  $\alpha\delta = \beta$ . Note  $\alpha \leq \beta$  means that  $\alpha$  is an initial part of  $\beta$ . The i<sup>th</sup> element in the sequence  $\alpha$  is denoted by  $\alpha_i$ ; the first element in the sequence  $\alpha$  is  $\alpha_i$ , provided  $\alpha \neq \Lambda$ . The length of the finite sequence  $\alpha$  is denoted by length  $\alpha$ . Note, if length  $\alpha$  and  $\alpha > 1$ , then  $\alpha = \alpha_1 \cdots \alpha_n$ .

Let ' $(x_1,...,x_k)$ ' be a typical element of the set  $\mathfrak{J}$ . We will use  $x_i[z]$ ' to denote  $a_i$  where  $z=(a_1,...,a_k)$ .

### 2.3 TIMINGS

- 2. <u>Definition</u>. A <u>timing</u> for the process P is a finite or infinite sequence of actions of the process P.

- 3. <u>Definition</u>. Suppose that  $P = \langle A, \emptyset, w \rangle$  is a process. We will define a function value as follows:

- (1)  $\underline{\text{value}}_{\mathcal{O}}(\Lambda) = \mathbf{w}$ .

- (2) If  $\alpha$  is a finite timing for P and f is an action in P,

then value  $P(\alpha f) = f[value_{P}(\alpha)]$ .

When there is no confusion we will delete the subscript 'P'. The function value, maps timings to elements in  $\mathfrak{N}$ . For example, value(fg) =g(f(w)).

We can think of the actions in a given timing as being "executed" in that order. Different timings correspond to "executing" the actions in a different order. Thus, value( $\alpha_1 \dots \alpha_n$ ) is the result of "executing" the actions in the order  $\alpha_1, \dots, \alpha_n$ . Note, the result of "executing"  $\Lambda$  is the initial data structure element w.

Any sequence of actions is a timing; hence, in a given process, we may consider some timings as "uninteresting". In the next section we will study the concept of scheduler; this concept allows us to consider certain special sets of timings.

# 2.4 FEATURES OF PROCESSES USED IN THE SYNCHRONIZATION AREA

One of our goals is to be able to model the processes used in the synchronization area, such as PV processes. In order to achieve this goal we will add additional structure to the model of the process concept as defined in Section 2.1; this structure must reflect the features of the processes used in the synchronization area. Therefore, we will examine the principal features of these processes.

The data structure of the processes in the synchronization area has three basic components.

- the syntactic representation of a process. For instance, the par begin-par end and co begin-co end notation of Dijkstra [1968] and Hoare [1971] are used to implicitly define several distinct program counters. We uniformly use 'L' with or without subscripts to denote a program counter.

- (2) program variables. These variables are usually explicit in the syntactic representation of a process. For example, the processes in Courtois, Heymans, Parnas [1971] and Brinch Hansen [1972] use program variables.

- (3) semaphores. These variables are usually explicit in the syntactic representation of a process. They are used exclusively in the inter-process communication of the process.

The actions of the processes in the synchronization area have several important features.

- (4) The actions of a process are divided into disjoint sets.

Each of these sets is the collection of all actions that

use a given program counter.

- (5) The actions of a process are also classified into two groups. The first group consists of the actions that handle the inter-process communication of the process.

These actions are usually called synchronizing primitives.

They are the only actions that can test or set the semaphore variables. The second group consists of the remaining actions. They are the only actions that can test or set the program variables.

- (6) The synchronizing primitives are usually actions of the form

- (a) when L = address  $\wedge$  p(E) do L  $\leftarrow$  new address; E  $\leftarrow$  q(E)

where L is a program counter, E is the part of the data structure that contains the semaphores, p is a predicate, and q is a function. The pairs (p,q) we allow in (a) distinguish the different synchronizing primitives. For example, the pair  $(x > 0, y \leftarrow y-1)$  is not allowed in PV processes; it is allowed in up/down processes (Wodon [1972]).

(7) The non-synchronizing primitives are usually actions of the form

when L = address do L  $\leftarrow$  b(D); D  $\leftarrow$  t(D)

where L is a program counter, D is the part of the data structure that contains the program variables, b is a function, and t is a function. Since b is a function, we allow these actions to branch, i.e.,

when L = 1 do  $L \leftarrow if x = 0$  then 2 else 3

is an acceptable action from this group. The actions in this group also satisfy an additional requirement. Suppose that f and g are actions in this group, f and g use different program counters, and f and g "share a variable". (In our model, f and g share a variable iff for some x in the data structure,  $f(g(x)) \neq g(f(x))$ .) Then the usual definition of processes in the synchronization area forces f and g to be "enclosed in critical sections". (In our model f and g are enclosed in critical sections iff for all finite timings  $\alpha$ , if  $f(\text{value}(\alpha)) \neq \text{value}(\alpha)$ , then  $g(\text{value}(\alpha)) = \text{value}(\alpha)$ .)

## 2.5 C PROCESSES

4. <u>Definition</u>. A set of pairs C is a <u>predicate system</u> provided, for each (p,q) in C, there exists a set E such that p is a predicate on E and q is a function from E to E. We will use C to denote a predicate system.

- 5. Definition. Let C be a predicate system. Also let  $P = \langle A, \emptyset, w \rangle$  be a process, and let ' $(L_1, \dots, L_n, D, E)$ ' be a typical element of  $\emptyset$ .

The process P is a C process if there is a predicate synchronizer on A, a function program-counter from A to  $\{1, \dots, n\}$ , and a function address with domain A such that

- (1) If not synchronizer(f), then there exists functions b and

t such that

- (a)  $f = \underline{when} L_k = address(f) \underline{do} L_k \leftarrow b(D); D \leftarrow t(D)$ where k = program-counter(f),

- (b) for all x in  $\mathfrak{I}$ , b(D[x])  $\neq$  address (f).

- (2) If synchronizer(f), then there exists a (p,q) ∈ C, called the pair of f, and a y such that

- (a)  $f = \underline{\text{when}} L_k = \text{address}(f) \land p(E) \underline{\text{do}} L_k \leftarrow y; E \leftarrow q(E)$ where k = program-counter(f).

- (b) y \( \nu \) address(f).

- (3) If not synchronizer(f), program-counter(f) ≠ program-counter(g),

and α is a finite timing, then

$f(g(value(\alpha))) = g(f(value(\alpha))).$

(4) If address(f) = address(g) and program-counter(f) = program-counter(g), then f = g.

The definition of C processes is motivated by our desire to be able

to model the processes used in the synchronization area. We will now relate the definition of C processes to the discussion in Section 2.4.

The data structure of a C process is composed of three parts.

- (1) program counters. These variables are  $L_1, \ldots, L_n$ .

- (2) program variables. The program variable is D. Since we make no restrictions on the range of the variable D, there is no loss in generality in considering all the program variables as one composite variable.

- (3) semaphores. The semaphores are considered as one composite variable E. As in (2), there is no loss in generality.

Thus, the data structure of a C process corresponds to the data structure of the processes used in the synchronization area. We now focus our attention on the actions of a C process.

- (4) The actions that use program counter L<sub>k</sub> are {f | program-counter(f) = k}. Each action is in exactly one of these sets.

- (5) The predicate synchronizer classifies the actions into two groups. If synchronizer(f), then f can test or set E, but it cannot test or set D. On the other hand, if not synchronizer(f), then f can test or set D, but it cannot test or set E.

- (6) If synchronizer(f), then f is equal to

when  $L_k = address(f) \land p(E) do L_k \leftarrow y$ ;  $E \leftarrow q(E)$

where k = program-counter(f) and  $(p,q) \in C$ . The pairs allowed in C determine the kinds of "synchronizers" that are allowed. In the next section we will define several predicate systems C.

(7) If not synchronizer(f), then f is equal to

when

$$L_k = address(f) \underline{do} L_k \leftarrow b(D); D \leftarrow t(D)$$

where k = program-counter(f). The additional requirement

stated in part (7) of Section 2.4 is reflected in condition

(3) of the definition of a C process. In fact, we can

prove the following

(a) Suppose that P satisfies the definition of a C process except that condition (3) is replaced by:

if f and g share a variable, then they are enclosed in critical sections. Then condition (3) is true.

For suppose that condition (3) is false; moreover, suppose that not synchronizer(f), program-counter(f)  $\neq$  program-counter(g), and  $f(g(value(\alpha))) \neq g(f(value(\alpha)))$ . If synchronizer(g), then  $f(g(value(\alpha))) = g(f(value(\alpha)))$ ; hence, not synchronizer(g). By assumption, f and g are enclosed in critical sections. In our model this is equivalent to

(b) if  $f(value(\beta)) \neq value(\beta)$ , then  $g(value(\beta)) = value(\beta)$ .

Informally, if f can "change the data structure element that results after executing  $\beta$ ", then g cannot "change the data structure element that results after executing  $\beta$ ". The contrapositive of (b) is

(b') if  $g(value(\beta)) \neq value(\beta)$ , then  $f(value(\beta)) = value(\beta)$ .

Thus, by symmetry, we can assume that  $g(value(\alpha)) = value(\alpha)$ .

Then  $f(g(value(\alpha))) = f(value(\alpha))$ . Since f cannot change

L where k = program-counter(g),  $g(value(\alpha f)) = value(\alpha f)$ .

Therefore,  $g(f(value(\alpha))) = f(value(\alpha))$ ; hence,  $f(g(value(\alpha))) = g(f(value(\alpha)))$ . This is a contradiction, and hence (a) is true.

Thus, the actions of C processes have the basic features as outlined in Section 2.4. Additional evidence that C processes are a reasonable model of synchronization processes is contained in Theorem 12.

#### 2.6 EXAMPLES OF PREDICATE SYSTEMS

- 6. <u>Definition</u>. The pair (p,q) is in the PV predicate systems iff there are non-negative integers i and k such that p is a predicate on  $E = \mathbb{Z}^k$  and either ( $\mathbb{Z}$  is the set of integers)

- (1)  $p(x_1...x_k)$  is always true, and  $q(x_1...x_k) = (x_1...x_{i-1}y x_{i+1}...x_k)$ where  $y = x_i + 1$ , or

- (2)  $p(x_1...x_k)$  is true iff  $x_i > 0$ , and  $q(x_1...x_k) = (x_1...x_{i-1}y_{i+1}...x_k)$ where  $y = x_i - 1$ .

In case (1), we say (p,q) is a  $V(x_i)$ ; in case (2), we say (p,q) is a  $P(x_i)$ .

Suppose that f is an action in a PV process and that synchronizer(f) is true. If the pair of f is a  $V(x_i)$ , then f is of the form

when

$$L_k = address(f) \underline{do} L_k \leftarrow z; x_i \leftarrow x_i + 1.$$

On the other hand, if the pair of f is a  $P(x_i)$ , then f is of the form

when

$$L_k = address(f) \land x_i > 0 \text{ do } L_k \leftarrow z; x_i \leftarrow x_i - 1.$$

The PV predicate system is essentially due to Dijkstra [1968]. Since he defines PV on an informal level, we cannot prove that our notion of PV processes corresponds exactly to his. However, we feel that our definition is a reasonable one.

7. <u>Definition</u>. The pair (p,q) is in the up/down predicate system iff there are non-negative integers i,k and a subset F of  $\{1,\ldots,k\}$  such that p is a predicate on  $E = \mathbb{Z}^k$  and either

(1)

$$p(x_1...x_k)$$

is  $\sum_{j \in F} x_j \ge 0$ , and  $q(x_1...x_k) = (x_1...x_{i-1}y \times_{i+1}...\times_k)$

where  $y = x_i + 1$ , or

(2)

$$p(x_1...x_k)$$

is  $\sum_{j \in F} x_j \ge 0$ , and  $q(x_1...x_k) = (x_1...x_{i-1}y x_{i+1}...x_k)$

where  $y = x_i - 1$ .

In case (1), we say (p,q) is a  $\frac{\{x_n | n \in F\}: up(x_i)}{i}$ ; in case (2), we say (p,q) is a  $\{x_n | n \in F\}: down(x_i)$ .

Suppose that f is an action in an up/down process and that synchronizer(f) is true. If the pair of f is a  $\{x_1,x_3\}$ : up $(x_4)$ , then f is of the form

. when

$$L_k = address(f) \wedge x_1 + x_3 \ge 0$$

do  $L_k \leftarrow z$ ;  $x_4 \leftarrow x_4 + 1$ .

As another example, if the pair of f is a  $\{x_1\}$ : down $(x_2)$ , then f is of the form

when

$$L_k = address(f) \land x_1 \ge 0 \text{ do } L_k \leftarrow z; x_2 \leftarrow x_2 - 1.$$

The predicate system up/down is essentially due to Wodon [1972]. He defines up/down on an informal level; hence, we cannot prove that our definition corresponds exactly to his definition. Indeed, we do not allow actions of the form

when

$$L_k = address(f) \land \sum_{j \in F} x_j \ge do L_k \leftarrow b(D); D \leftarrow t(D)$$

while he does. An action of this form violates what we stated in part 5 of Section 2.4: these actions can test semaphores and test and set program variables. Also, these actions do not satisfy the main theorem of this section - Theorem 12. For these reasons we will not change our definition of up/down processes.

- 8. <u>Definition</u>. The pair (p,q) is in the <u>PVchunk</u> predicate system iff there are non-negative integers i,k,m such that p is a predicate on  $E = \mathbb{Z}^k$  and either

- (1)  $p(x_1...x_k)$  is always true, and  $q(x_1...x_k) = (x_1...x_{i-1}y x_{i+1}...x_k)$ where  $y = x_i + m$ , or

- (2)  $p(x_1...x_k)$  is true iff  $x_i \ge m$ , and  $q(x_1...x_k) = (x_1...x_{i-1}y \times_{i+1}...\times_k)$ where  $y = x_i - m$ .

In case (1), we say that (p,q) is a  $V(x_i)$  with amount m); in case (2), we

say that (p,q) is a  $P(x_i)$  with amount m).

Suppose that f is an action in a PVchunk process and that synchronizer(f) is true. For example, if the pair of f is a  $V(x_3)$  with amount 5), then f is of the form

when

$$L_k = address(f) do L_k \leftarrow z$$

;  $x_3 \leftarrow x_3 + 5$ .

As another example, if the pair of f is a  $P(x_2 \text{ with amount 3})$ , then f is of the form

when

$$L_k = address(f) \land x_2 \ge 3 \text{ do } L_k \leftarrow z; x_2 \leftarrow x_2 - 3.$$

The predicate system PVchunk is essentially due to Vantilborgh and van Lamsweerde [1972]. Again we can only assert that out PVchunk processes are a reasonable model of their processes.

- 9. <u>Definition</u>. The pair (p,q) is in the <u>PVmultiple</u> predicate system iff there is a non-negative integer k and a subset F of  $\{1,\ldots,k\}$  such that p is a predicate on  $E = \mathbb{Z}^k$  and either

- (1)  $p(x_1...x_k)$  is always true, and  $q(x_1...x_k) = (y_1...y_k)$ where  $y_i = \underline{if} \ i \in F \underline{then} \ x_i + 1 \underline{else} \ x_i$ , or

- (2)  $p(x_1...x_k)$  is true iff [for  $i \in F$ ,  $x_i \ge 1$ ], and  $q(x_1...x_k) = (y_1...y_k) \text{ where } y_i = \underline{if} \ i \in F \ \underline{then} \ x_i 1 \ \underline{else} \ x_i.$

In case (1), we say that (p,q) is a  $V(\{x_n | n \in F\})$ ; in case (2), we say that (p,q) is a  $P(\{x_n | n \in F\})$ .

Suppose that f is an action in a PVmultiple process and that synchronizer(f) is true. For example, if the pair of f is  $V(\{x_1,x_2\})$ ,

then f is of the form

when

$$L_k = address(f) \underline{do} L_k \leftarrow z$$

;  $x_1 \leftarrow x_1 + 1$ ;  $x_2 \leftarrow x_2 + 1$ .

As another example, if the pair of f is a  $P(\{x_1,x_3\})$ , then f is of the form

when

$$L_k = address(f) \land x_1 \ge 1 \land x_3 \ge 1 \text{ do } L_k \leftarrow z; x_1 \leftarrow x_1 - 1;$$

$$x_3 \leftarrow x_3 - 1.$$

The predicate system PVmultiple is essentially due to Patil [1971] and Dijkstra [unpublished]. Again we can only assert that our PVmultiple processes are a reasonable model of the processes informally defined by Patil and Dijkstra.

The predicate system PV is a subset of both the predicate system PVchunk and the predicate system PVmultiple. Suppose that (p,q) is a  $V(x_i)$ . Then (p,q) is a  $V(x_i)$  with amount 1), and (p,q) is a  $V(\{x_i\})$ . Thus, (p,q) is in PVchunk and PVmultiple. On the other hand, suppose that (p,q) is a  $P(x_i)$ . Then (p,q) is a  $P(x_i)$  with amount 1), and (p,q) is a  $P(\{x_i\})$ . Therefore,  $PV \subseteq PV$ chunk and  $PV \subseteq PV$ multiple. As a consequence,

the set of PV processes ⊆ the set of PVchunk processes and the set of PV processes ⊆ the set of PVmultiple processes.

The relationship between the predicate system PV and the predicate system up/down is complex. Clearly, PV is not a subset of up/down: the pair  $(x > 0, x \leftarrow x - 1)$  is not in up/down. However, as Wodon [1972] correctly states: each PV process is "equivalent or isomorphic" to an

up/down processes. We shall state a relation between PV processes and up/down processes in section 4; in this section we study relations between processes.

Many of the processes used in the synchronization area can be considered as C processes, for a suitable predicate system C. These processes include: fork-join processes (Dennis and Van Horn [1966]), block-wakeup (Saltzer [1966]), conditional critical sections (Brinch Hansen [1972]), and certain Petri Nets (Patil [1971]).

#### 2.7 REPRESENTATION OF C PROCESSES

We will use several conventions when we define C processes. These conventions are best explained by an example. Process EX1 - a PV process - is defined in Figure 2.

program counter L1, L2; (initial value 1)

integer x,y; (initial value 0)

semaphore S; (initial value 1)

SUBPROCESS-1

- (1) when  $L_1 = 1 \land S \ge 1$  do  $L_1 \leftarrow 2$ ;  $S \leftarrow S 1$

- (2) when  $L_1 = 2$  do  $L_1 \leftarrow 3$ ;  $x \leftarrow 1$

- (3) when  $L_1 = 3$  do  $L_1 \leftarrow 4$ ;  $S \leftarrow S + 1$

SUBPROCESS-2

- (4) when  $L_2 = 1 \land S \ge 1$  do  $L_2 \leftarrow 2$ ;  $S \leftarrow S 1$

- (5) when  $L_2 = 2$  do  $L_2 \leftarrow 3$ ;  $y \leftarrow x$

- (6) when  $L_2 = 3$  do  $L_2 \leftarrow 4$ ;  $S \leftarrow S + 1$

FIGURE 2. Process EX1: formal representations

Several conventions have been used in Figure 2. First, the data structure of EX1 has been defined in an implicit way. The data structure of EX1 is

$$\mathbb{Z} \times \mathbb{Z} \times \mathbb{Z}^2 \times \mathbb{Z}$$

Let ' $(L_1, L_2, D, E)$ ' be a typical element of the data structure of EX1. Then  $L_1, L_2$ , E range over integers while D ranges over pairs of integers. D ranges over pairs of integers because we consider the program variables x,y as one composite variable D. Second, the initial data structure element of EX1 has been defined in an implicit way. The initial data structure element is (1,1,(0,0),1). Third, the actions of EX 1 have been numbered for future reference. Thus, action 3 is

when

$$L_1 = 3 \text{ do } L_1 - 4$$

;  $S - S + 1$ .

Fourth, the sets of actions that use each program counter have been given names. Thus, SUBPROCESS-2 contains the actions 4,5,6.

These conventions will be used whenever we define a C process.

Although the conventions are stated informally, the translation to a precisely defined C process should be clear.

The syntactic representation of process EX1 in the style of Courtois, Heymans, Parnas [1971] is displayed in Figure 3. Figure 3 deletes all references to program counters. Moreover, if synchronizer(f), then action f is represented by just the pair of f. Thus,

when

$$L_1 = 1 \land S \ge 1 \stackrel{\text{do}}{=} L_1 \leftarrow 2$$

;  $S \leftarrow S - 1$

is represented by P(S). Although process EX1 is a PV process, we can also consider it as a PVchunk process. In this case, action 1 is represented by P(S with amount 1).

integer x,y; (initial value 0)

semaphore S; (initial value 1)

SUPROCESS-1

SUBPROCESS-2

(1) P(S);

(2) x := 1;

(5) y := x;

(3) V(S);

(6) V(S);

FIGURE 3. Process EX1: informal representation

# 2.8 SUBPROCESS, READY-SET, POINTER-SET

We will now define three notions: subprocess, ready-set, pointerset. These notions satisfy two requirements.

- (1) They are rich enough to allow us to express most of our ideas about C processes.

- (2) They suppress a great many of the unnecessary or uninteresting details of C processes.

- 10. <u>Definition</u>. Suppose that  $P = \langle A, \mathfrak{J}, w \rangle$  is a C process, and let '(L<sub>1</sub>,...,L<sub>n</sub>,D,E)' be a typical element of  $\mathfrak{J}$ .

- (1) For actions f and g, subprocess (f,g) iff program-counter(f) =

program-counter(g). Subprocess is an equivalence relation on

the actions of P. Let SUBPROCESS-i denote the i th equivalence

class of the relation subprocess, i.e., {f program-counter(f) = i}.

(3) An action f is in pointer-set  $\alpha$  where  $\alpha$  is a finite timing iff

$$L_{k}[value(\alpha)] = address(f)$$

where k = program-counter(f).

In each of these notions we will drop the subscript 'P' when this will cause no confusion.

The notions subprocess, ready-set, pointer-set have intuitive meanings. Suppose that  $P = \langle A, \emptyset, w \rangle$  is a C process, and let '(L<sub>1</sub>,...,L<sub>n</sub>,D,E)' be a typical element in  $\emptyset$ . Recall that L<sub>1</sub>,...,L<sub>n</sub> are program counters.

- (1) Subprocess divides A into the disjoint sets SUBPROCESS-1,..., SUBPROCESS-n. SUBPROCESS-i is the set of actions that use the program counter L<sub>i</sub>.

- (2) Ready-set( $\alpha$ ) is the set of actions that can "change the data structure element that results after executing the timing  $\alpha$ ". For example, if f is

when

$$L_3 = 2 \land S \ge 3$$

do  $L_3 \leftarrow 3$ ;  $S \leftarrow S - 3$ ,

then f is in the ready-set( $\alpha$ ) iff

$$L_3[value(\alpha)] = 2$$

and  $S[value(\alpha)] \ge 3$ .

As another example, suppose that f is a "nop or null statement", i.e.,

$$f = \underline{\text{when}} L_k = \text{address}(f) \underline{\text{do}} L_k \leftarrow z.$$

Then f is in ready-set(a) iff  $L_k[value(a)]$  is equal to address(i). This example is interesting because f never changes any program variables or semaphores. However, in our model f can change the data structure; for our concept of data structure includes the program counters.

(3) Pointer-set(α) is the set of actions f such that the program counter of f "points to f". For example, if f is

when

$$L_3 = 2 \land S \ge 3$$

do  $L_3 \leftarrow 3$ ;  $S \leftarrow S - 3$ ,

then f is in the pointer-set( $\alpha$ ) iff

$$L_3[value(\alpha)] = 2.$$

The notions subprocess, ready-set, pointer-set are sufficient.

to express the basic concepts of the synchronization area. For

instance, these notions can express the concept of "PV release mechanism"

as defined by Dijkstra [1968] and the concept of "fairness"; this is

demonstrated in Section 3. In addition we will show, in Section 4,

how we can use these three notions to express the concepts of "safe"

and "deadlock free". One of the contributions of our model is the

understanding that the notions subprocess, ready-set, pointer-set are

sufficient to express the central features of the synchronization area.

# 2.9 BASIC PROPERTIES OF C PROCESSES

We will now state and then prove four basic properties shared by

all C processes. These properties do not depend on the predicate system

C. The proof of these properties should help motivate each decision that

has been made in the definition of C processes.

11. <u>Definition</u>. The timing  $\alpha$  is <u>active</u> in a C process provided, if  $\beta f \leq \alpha$ , then f is in ready-set  $(\beta)$ .

The timing  $\alpha_1 \cdots \alpha_n$  is active if and only if for each i,  $\alpha_i$  is in ready-set  $(\alpha_1 \cdots \alpha_{i-1})$ . Informally, the timing  $\alpha_1 \cdots \alpha_n$  is active if and only if each action  $\alpha_i$  can change the data structure element that results "after executing  $\alpha_1 \cdots \alpha_{i-1}$ ".

- (I) For any finite timing α, ready-set(α) ⊆ pointer-set(α).

This property is an immediate consequence of the defintion of a C

process. Informally, if the action f can "run", then the program counter

of f must "point" to f.

- (II) For any finite timing  $\alpha$ , the pointer-set( $\alpha$ ) has at most one action from each SUBPROCESS-i.

This property is a direct consequence of condition 4 of Definition 5. For suppose that f and g are in pointer-set( $\alpha$ ) and subprocess (f,g). Then by definition of subprocess, program-counter(f) = program-counter(g). By the definition of pointer-set,

$L_{program-counter(f)}[value(\alpha)] = address(f)$  and  $L_{program-counter(g)}[value(\alpha)] = address(g)$ .

Thus, address(f) = address(g), and hence by condition (4) of Definition 5, f = g.

We have excluded actions of the kind

$$f = \underline{\text{when}} L_1 = 1 \land S > 0 \underline{\text{do}} L_1 \leftarrow 2$$

$g = \underline{\text{when}} L_1 = 1 \land S = 0 \underline{\text{do}} L_1 \leftarrow 3$

from C processes. We have to express f and g as

when

$$L_1 = 1$$

do  $L_1 \leftarrow if S = 0$  then 2 else 3.

(III) If  $\alpha f \beta$  and  $\alpha \beta$  are active finite timings, then

pointer-set( $\alpha$ f $\beta$ )  $\cap$  SUBPROCESS-i = pointer-set( $\alpha$  $\beta$ )  $\cap$  SUBPROCESS-i

provided f is not in SUBPROCESS-i. [N is set intersection]

This property is non-trivial; it will be proved in detail in Theorem

12. This property allows us to compare the pointer-sets of distinct active timings. It states that the program counters are in some sense

"local". Actions from SUBPROCESS-i cannot change the program counters of

SUBPROCESS-j, provided i # j.

(IV) If  $\alpha f \beta \delta$  and  $\alpha \beta f \delta$  are active finite timings, then

pointer-set( $\alpha f \beta \delta$ ) = pointer-set( $\alpha \beta f \delta$ ).

This property is also non-trivial; it will be proved in detail in

Theorem 12. This property also allows us to compare the pointer-sets

of distinct active timings. It states that the pointer-set has a certain

kind of "order invariance".

12. Theorem. Every C process satisfies properties I-IV.

<u>rroof.</u> Let  $P = \langle A, \mathfrak{I}, w \rangle$  be a C process. Let '(L<sub>1</sub>,...,L<sub>n</sub>,D,E)' be a typical element in  $\mathfrak{I}$ .

Lemma 1. Suppose that x is in  $\mathfrak{J}$ , f is an action, and  $1 \le k \le n$ . Then

- (1) if program-counter(f)  $\neq k$ , then  $L_k[x] = L_k[f(x)]$

- (2) if  $f(x) \neq x$ , then  $L_{program-counter(f)}[x] = address(f)$ .

Proof of Lemma. This is an immediate consequence of the definition of

a C process. □

Lemma 2. Suppose that x is in  $\mathfrak{J}$ , y is in  $\mathfrak{J}$ , and  $1 \le k \le n$ . Also suppose that D[x] = D[y] and  $L_k[x] = L_k[y]$ . Then if  $f(x) \ne x$  and  $f(y) \ne y$  where **f** is an action, then D[f(x)] = D[f(y)] and  $L_k[f(x)] = L_k[f(y)]$ .

Proof of Lemma. This is also an immediate consequence of the definition of a C process.

Lemma 3. Suppose that  $\alpha\beta$  and  $\lambda\beta$  are finite active timings. Also suppose that  $D[value(\alpha)] = D[value(\lambda)]$  and  $L_k[value(\alpha)] = L_k[value(\lambda)]$ . Then  $D[value(\alpha\beta)] = D[value(\lambda\beta)]$  and  $L_k[value(\alpha\beta)] = L_k[value(\lambda\beta)]$ .

Proof of Lemma. This follows by repeated applications of Lemma 2.

Lemma 4. Suppose that  $\alpha f \beta$  and  $\alpha \beta$  are finite active timings. Then for  $1 \le i \le length(\beta)$ , program-counter(f)  $\neq$  program-counter( $\beta_i$ ).

<u>Proof of Lemma</u>. Let k = program-counter(f). Assume that the lemma is false, and let i be the least integer such that k = program-counter( $\beta_i$ ).

By Lemma 1, part 2, since  $\alpha f$  and  $\alpha \beta_1 \dots \beta_{i-1} \beta_i$  are active,

$$L_{\mathbf{k}}[value(\alpha)] = address(f)$$

and  $L_{\mathbf{k}}[value(\alpha\beta_{1}...\beta_{i-1})] = address(\beta_{i}).$

By Lemma 1, part 1 and the definition of i, an inductive argument shows that

$$L_{k}[value(\alpha)] = L_{k}[value(\alpha\beta_{1}...\beta_{i-1})].$$

Hence, address(f) = address( $\beta_i$ ). Therefore, by the definition of a C process,  $f = \beta_i$ . By the definition of a C process (1b and 2b),

$$L_{\mathbf{k}}[value(\alpha f)] \neq address(f).$$

By Lemma 1, part 1 and the definition of i,

$$L_{k}[value(\alpha f \beta_{1} ... \beta_{i-1})] = L_{k}[value(\alpha f)] \neq address (f).$$

But  $\alpha f \beta_1 \cdots \beta_{i-1} \beta_i$  is active, so by Lemma 1, part 2,

•

$$L_k[value(\alpha f \beta_1 ... \beta_{i-1})] = address(\beta_i)$$

.

This is a contradiction, for  $f = \beta_i$ .  $\square$

By what we have already shown, we need only prove that a C process satisfies properties III and IV.

We will now show that property III is satisfied by P. Suppose that  $\alpha f \beta$  and  $\alpha \beta$  are finite active timings. In order to prove property III, it is sufficient to prove

(3) for

$$i \neq k$$

,  $L_i[value(\alpha f \beta)] = L_i[value(\alpha \beta)]$

where k = program-counter(f). For suppose that (3) is true. Let g be

an action such that not subprocess (f,g). Now g is in pointer-set( $\alpha$ f $\beta$ ) iff

$$L_{i}[value(\alpha f \beta)] = address(g)$$

where j = program-counter(g). Also g is in pointer-set( $\alpha\beta$ ) iff

$$L_{j}[value(\alpha\beta)] = address(g).$$

Since  $k \neq j$  and (3) is true,

g is in pointer-set( $\alpha$ f $\beta$ ) iff g is in pointer-set( $\alpha$  $\beta$ ).

Therefore, property III is true; hence condition (3) implies property III.

In proving (3), there are two cases depending whether or not synchronizer(f) is true. First, suppose that not synchronizer(f). By repeated applications of condition (3) in the definition of a C process and the fact that, by Lemma 4,

for  $1 \le j \le length(\beta)$ ,  $k \ne program-counter(\beta_j)$ ,

we can conclude that value( $\alpha f \beta$ ) = value( $\alpha \beta f$ ). By Lemma 1, part 1,

for  $i \neq k$ ,  $L_i[value(\alpha\beta)] = L_i[value(\alpha\beta f)]$ .

Thus, in this case (3) is true. Second, suppose that synchronizer(f).

By the definition of a C process and Lemma 1, part 1,

$D[value(\alpha)] = D[value(\alpha f)]$  and for  $i \neq k$ ,  $L_i[value(\alpha)] = L_i[value(\alpha f)]$ .

By Lemma 3,

$D[value(\alpha\beta)] = D[value(\alpha f\beta)]$  and for  $i \neq k$ ,  $L_i[value(\alpha\beta)] = L_i[value(\alpha f\beta)]$ .

Thus, in this case (3) is true. Therefore, P satisfies property III.

We will now prove that P satisfies property IV. Suppose that  $\alpha f\beta \delta$  and  $\alpha \beta f\delta$  are finite active timings. In order to prove property IV, it is sufficient to prove that

(4) for all i,  $L_i[value(\alpha f \beta \delta)] = L_i[value(\alpha \beta f \delta)]$ .

For suppose that (4) is true. Let g be an action. Then g is in pointerset( $\alpha f \beta \delta$ ) iff

$L_j[value(\alpha f \beta \delta)] = address(g)$

where j = program-counter(g). Also g is in pointer-set( $\alpha\beta f \delta$ ) iff

$L_{j}[value(\alpha\beta f \delta)] = address(g).$

Since (4) is true,

g is in pointer-set( $\alpha f \beta \delta$ ) iff g is in pointer-set( $\alpha \beta f \delta$ ).

Therefore, property IV is true; hence, condition (4) implies property IV.

In proving (4), there are two cases depending whether or not synchronizer(f) is true. First, suppose that not synchronizer(f). By repeated applications of condition (3) in the definition of a C process and Lemma 4, we can conclude as before that value( $\alpha f \beta$ ) = value( $\alpha f \beta$ ). Thus, value( $\alpha f \beta \delta$ ) = value( $\alpha f \delta$ ), and hence (4) is true. Second, suppose that synchronizer(f). As in the proof of property III we can show that

$D[value(\alpha\beta)] = D[value(\alpha f\beta)]$  and

for all

$$i \neq k$$

,  $L_i[value(\alpha\beta)] = l_i[value(\alpha\beta)]$

where k = program-counter(f). By the definition of a C process and

Lemma 1, part 1,

D[value(

$$\alpha\beta$$

f)] = D[value( $\alpha$ f $\beta$ )] and

for i \( \neq \kappa\_i \) L\_i[value( $\alpha$ f $\beta$ )] = L\_i[value( $\alpha$ f $\beta$ )].

Since synchronizer(f), there is a constant, say z, such that

if

$$f(x) \neq x$$

, then  $L_k[f(x)] = z$ .

Thus,  $L_k[value(\alpha f)] = z$  and  $L_k[value(\alpha f)] = z$ . By Lemma 4 and Lemma 1, part 1,

$$L_{\mathbf{k}}[value(\alpha f \beta)] = L_{\mathbf{k}}[value(\alpha f)].$$

Therefore,

$$D[value(\alpha \beta f)] = D[value(\alpha f \beta)]$$

and

for all i,  $L_i[value(\alpha \beta f)] = L_i[value(\alpha f \beta)]$ .

Finally, by Lemma 3,

for all i,

$$L_i[value(\alpha \beta f \delta)] = L_i[value(\alpha f \beta \delta)]$$

.

Thus, in this case, (4) is true. Thus, P satisfies property IV.

# 2.10 REMARKS ON THE PROPERTIES I-IV

We will now present an example of a PV process that shows that certain generalizations of properties III and IV do not hold for PV processes. The formal representation of process EX2 is in Figure 4.

```

program counter L1, L2; (initial value 0)

integer x,y; (initial value 0)

semaphore m; (initial value 1)

SUBPROCESS-1

(1) when L_1 = 0 \land m > 0 do L_1 \leftarrow 1; m \leftarrow m - 1

(2) when L_1 = 1

\underline{do} \ L_1 \leftarrow 2; \ x \leftarrow 1

(3) when L_1 = 2 do L_1 \leftarrow 3; m \leftarrow m + 1

SUBPROCESS-2

(4) when L_2 = 0 \land m > 0 \text{ do } L_2 \leftarrow 1; m \leftarrow m - 1

\underline{do} \ L_2 \leftarrow 2; \ y \leftarrow x

\underline{do} \ L_2 \leftarrow 3; \ m \leftarrow m + 1

(5) when L_2 = 1.

(6) when L_2 = 2 do L_2 \leftarrow 3, when L_3 = 3 do L_2 \leftarrow if y = 0 then 4 else 5

(8) when L_2 = 4

\underline{do} L_2 \leftarrow 5

(9) when L_2 = 5 do L_2 \leftarrow 6

```

FIGURE 4. Process EX2: formal representation

The informal representation of P is displayed in Figure 5.

```

semaphore m; (initial value 1)

SUBPROCESS-1

(1) P(m);

(2) x := 1;

(3) V(m);

SUBPROCESS-2

(4) P(m);

(5) y := x;

(6) V(m);

(7) if y = 0 then goto A else goto B;

(8) A:;

(9) B:;

FIGURE 5. Process EX2: informal representation

```

integer x,y; (initial value 0)

First, let us consider the following generalization of property

III:

(1) if  $\alpha\lambda\beta$  and  $\alpha\beta$  are finite active timings and each action in  $\lambda$  is in SUBPROCESS-i, then pointer-set( $\alpha\lambda\beta$ )  $\cap$  SUBPROCESS-j = pointer-set( $\alpha\beta$ )  $\cap$  SUBPROCESS-j, provided i  $\neq$  j.

By the definition of the process EX2, pointer-set(4567) = {1,8} and pointer-set(1234567) = {9}. Thus, (1) is false, since pointer-set(4567) \(\Omega\) SUB-PROCESS-2 = {8} and pointer-set(1234567) \(\Omega\) SUBPROCESS-2 = {9}. Therefore, this generalization of property III does not hold for PV processes.

Second, let us consider the following generalization of property IV:

(2) if  $\alpha$  and  $\beta$  are finite active timings and  $\alpha$  is a permutation of  $\beta$ , then pointer-set( $\alpha$ ) = pointer-set( $\beta$ ).

By the definition of process EX2, pointer-set(1234567) = {9} and pointer-set(4567123) = {8}. Since 1234567 is a permutation of 4567123, this generalization does not hold for PV processes.

These two examples show how delicate the two properties III and IV are. The chief difficulty we had in proving these properties, in Theorem 12, was due to the fact that we allow conditionals in our C processes.

Any reasonable theory or model of PV processes must allow conditionals.

For example, conditionals are used in the processes defined in Courtois, Heymans, Parnas [1971]. In addition, conditionals allow us to show that our definition of a PV process incorporates the notion of a "PV with array semaphores". A P on the array semaphore s(n) is equivalent to the actions

when  $L_k = a \cdot do \cdot L_k \leftarrow branch(n)$ when  $L_k = a_i \wedge S_i > 0 \cdot do \cdot L_k \leftarrow a'; S_i \leftarrow S_i - 1 \quad [1 \le i \le max].$

The value of branch(n) is equal to  $a_n$ . We have replaced an array P by a "branch action" and several P's; the same construction can be used for array V's.

The properties I-IV and the notions ready-set, pointer-set, and subprocess are of central importance. In fact, all our basic theorems

are proved using only these properties and these notions. The

only exceptions are the specific results in Section 7, i.e., our theorems about PV processes, PVchunk processes, PVmultiple processes, and up/

down processes. Our insistence on using only the properties I-IV and

the notions ready-set, pointer-set, and subprocess will now be demonstrated.

- 13. <u>Definition</u>. A set of actions in a process is <u>sequential</u> provided for all finite timings  $\alpha$ , at most one action from this set is in the ready-set( $\alpha$ ).

- 14. Theorem. Each subprocess-i of a C process is sequential.

<u>Proof.</u> Suppose that f and g are in SUBPROCESS-i, and suppose that f and g are in ready-set( $\alpha$ ). By property I, f and g are in pointer-set( $\alpha$ ).

Thus, by property II, f = g.

#### 3. SCHEDULERS

We will now define the concept of scheduler. This concept is used to state the theorem of Habermann [1972]. More importantly, the concept of scheduler displays the generality of our model.

1. <u>Definition</u>. Suppose that P is a process. Then S is a <u>scheduler</u> for P provided, S is a predicate on the timings of P.

We can use a scheduler S to select timings that satisfy a number of criterion. First, the scheduler S might "enforce a priority" among the actions of the process. For example, the actions that control a hardware. device may be given priority over the actions of a user's program. Second, the scheduler S might enforce "fairness" among the actions of the process. For instance, consider a disk queuer that uses the "least arm movement criterion" to select the next request. Often the scheduler is designed so that requests for a distance part of the disk do not wait forever. Third, the scheduler S might "enforce the release mechanism of PV" (Dijkstra [1968a]).

The separation of the notion of scheduler from the notion of process gives us a great deal of freedom. We are able to study the same process with respect to a variety of schedulers. We do not present one scheduler as the "correct one"; instead, we present and study several different schedulers.

### .3.1 SEMI-ACTIVE TIMINGS

- 2. <u>Definition</u>. A timing  $\alpha$  in a C process is <u>semi-active</u> provided, if  $\beta f \leq \alpha$ , then f is in pointer-set( $\beta$ ).

- 3. Theorem. Suppose that P is a C process and that the relation subprocess has m equivalence classes. Also suppose that  $N_1, \ldots, N_k$  are integers from the set  $\{1, \ldots, m\}$ . Then there is at most one semi-active timing  $\alpha$  such that

for  $1 \le i \le k$ ,  $\alpha_i$  is in SUBPROCESS-N<sub>i</sub>.

Proof. Immediate from property II. □

Theorem 3 is implicitly used in operating systems. They usually consider timings as sequences of "subprocess names" instead of as sequences of actions. The key observation is: as long as we are only interested in semi-active timings, it is immaterial whether we consider timings as sequences of subprocess names or as sequences of actions.

## 3.2 BLOCKING AND THE PV RELEASE SCHEDULER

It is instructive to consider the timing 13521 of the process EX3 (a formal representation of EX3 is in Figure 6). This timing is semi-active; it is not active. The "execution" of this timing is informally

- 1 this action changes  $L_1$  to 2 and a to 0

- 3 this action does not change the data structure it is now blocked

- 5 this action does not change the data structure it is now blocked

- 2 this action changes L, to 1 and a to 1

- 1 this action changes  $L_1$  to 2 and a to 0

program counter L<sub>1</sub>,L<sub>2</sub>,L<sub>3</sub>; (initial value 1)

semaphore a; (initial value 1)

**SUBPROCESS-1**

(1) when

$$L_1 = 1 \land a \ge 1 \text{ do } L_1 \leftarrow 2$$

;  $a \leftarrow a - 1$

(2) when

$$L_1 = 2$$

do  $L_1 \leftarrow 1$ ;  $a \leftarrow a + 1$

SUBPROCESS-2

(3) when

$$L_2 = 1 \land a \ge 1$$

do  $L_2 \leftarrow 2$ ;  $a \leftarrow a - 1$

(4) when

$$L_2 = 2$$

do  $L_2 \leftarrow 1$ ;  $a \leftarrow a + 1$

SUBPROCESS-3

(5) when

$$L_3 = 1 \land a \ge 1$$

do  $L_3 \leftarrow 2$ ;  $a \leftarrow a - 1$

(6) when

$$L_3 = 2$$

do  $L_3 \leftarrow 1$ ;  $a \leftarrow a + 1$

FIGURE 6. Process EX3: formal representation

The usual literature definition of PV (Dijkstra [1968a]) rules out this timing. The informal reason that the timing 13521 is not allowed is:

"P's that are blocked, i.e., 3 and 5, must be given priority over P's that are not blocked, i.e., 1". The way our model handles this restriction is that we can define a scheduler S such that

if a timing satisfies S, then the timing "gives blocked P's priority over other P's".

In particular, 13521 will not satisfy S.

- 4. <u>Definition</u>. Suppose that  $\alpha$  is a finite timing in a C process. Define <u>blocked-set( $\alpha$ )</u> inductively as follows.

- blocked-set(A) is the empty set.

- (2) If  $\alpha_k$  is not in ready-set $(\alpha_1 \cdots \alpha_{k-1})$  then blocked-set $(\alpha_1 \cdots \alpha_k)$  = blocked-set $(\alpha_1 \cdots \alpha_{k-1})$  U  $\{\alpha_k\}$ .

- (3) If  $\alpha_k$  is in ready-set $(\alpha_1 \cdots \alpha_{k-1})$ , then blocked-set $(\alpha_1 \cdots \alpha_k)$  = blocked-set $(\alpha_1 \cdots \alpha_{k-1})$  -  $\{\alpha_k\}$ .

Note, U is set union, and - is set difference.

Informally, the action  $\alpha_k$  is "added" to block-set $(\alpha_1 \cdots \alpha_{k-1})$  if  $\alpha_k$  cannot "run"; the action  $\alpha_k$  is "removed" from blocked-set $(\alpha_1 \cdots \alpha_{k-1})$  if  $\alpha_k$  can "run". For example, consider again the timing 13521 of the process EX3. Then blocked-set(1352) = {3,5}; this formalizes the intuitive statement made earlier.

In order for an action to be in blocked-set( $\alpha_1 \cdots \alpha_k$ ), it must have been "tried". More exactly, blocked-set( $\alpha_1 \cdots \alpha_k$ ) is a subset of  $\{\alpha_1, \ldots, \alpha_k\}$ . For instance, consider the timing 13 in process EX3. Clearly, blocked-set(13) =  $\{3\}$ . Note, action 5 is not in ready-set(13). However, action 5 is not in blocked-set(13); for it has not been tried.

We will only ever consider blocked-set( $\alpha$ ) for semi-active  $\alpha$ . For timings that are not semi-active, blocked-set( $\alpha$ ) can behave in strange ways. For instance, since (in process EX3) action 2 is not in ready-set( $\Lambda$ ), blocked-set(2) = {2}. However, it is definitely "pathological" to have a V(a) inserted into the blocked-set. This "pathology" can be avoided if we restrict our attention to semi-active timings. In fact we can prove in a PV process that

if f is in blocked-set( $\alpha$ ) and  $\alpha$  is semi-active, then f is a P(b), for some b.

- (2) If  $\alpha_k$  is not in ready-set $(\alpha_1 \cdots \alpha_{k-1})$  then blocked-set $(\alpha_1 \cdots \alpha_k)$  = blocked-set $(\alpha_1 \cdots \alpha_{k-1})$  U  $\{\alpha_k\}$ .

- (3) If  $\alpha_k$  is in ready-set $(\alpha_1 \cdots \alpha_{k-1})$ , then blocked-set $(\alpha_1 \cdots \alpha_k)$  = blocked-set $(\alpha_1 \cdots \alpha_{k-1})$   $\{\alpha_k\}$ .

Note, U is set union, and - is set difference.

Informally, the action  $\alpha_k$  is "added" to block-set $(\alpha_1 \cdots \alpha_{k-1})$  if  $\alpha_k$  cannot "run"; the action  $\alpha_k$  is "removed" from blocked-set $(\alpha_1 \cdots \alpha_{k-1})$  if  $\alpha_k$  can "run". For example, consider again the timing 13521 of the process EX3. Then blocked-set(1352) = {3,5}; this formalizes the intuitive statement made earlier.

In order for an action to be in blocked-set( $\alpha_1 \cdots \alpha_k$ ), it must have been "tried". More exactly, blocked-set( $\alpha_1 \cdots \alpha_k$ ) is a subset of  $\{\alpha_1, \ldots, \alpha_k\}$ . For instance, consider the timing 13 in process EX3. Clearly, blocked-set(13) =  $\{3\}$ . Note, action 5 is not in ready-set(13). However, action 5 is not in blocked-set(13); for it has not been tried.

We will only ever consider blocked-set( $\alpha$ ) for semi-active  $\alpha$ . For timings that are not semi-active, blocked-set( $\alpha$ ) can behave in strange ways. For instance, since (in process EX3) action 2 is not in ready-set( $\Lambda$ ), blocked-set(2) = {2}. However, it is definitely "pathological" to have a V(a) inserted into the blocked-set. This "pathology" can be avoided if we restrict our attention to semi-active timings. In fact we can prove in a PV process that

if f is in blocked-set( $\alpha$ ) and  $\alpha$  is semi-active, then f is a P(b), for some b.

5. Definition. A timing  $\alpha$  is a <u>release</u> timing in a C process provided, for  $\beta f \leq \alpha$ ,

if blocked-set( $\beta$ )  $\cap$  ready-set( $\beta$ ) is non-empty, then f is in blocked-set( $\beta$ )  $\cap$  ready-set( $\beta$ ).

Suppose that  $\alpha$  is a timing in a C process and  $\beta f \leq \alpha$ . Informally, the set of actions in the set blocked-set( $\beta$ )  $\cap$  ready-set( $\beta$ ) is the set of actions that satisfy

- (1) they can "run",

- (2) they were at "one time blocked",

- (3) they have never been "unblocked".

The release restriction is that if this set is non-empty, then f must be in blocked-set( $\beta$ )  $\cap$  ready-set( $\beta$ ). A release timing "enforces a kind of priority rule": the actions in blocked-set( $\beta$ )  $\cap$  ready-set( $\beta$ ) have a "priority" over all other actions. However, there is no priority among the actions in blocked-set( $\beta$ )  $\cap$  ready-set( $\beta$ ).

Let us return once again to the timing 13521 of process EX3.

The objection stated earlier is: 13521 is not a release timing.

Both 13523 and 13525 are release timings. The release restriction enforces no priority based on "the order an action is added to blocked-set".

Most discussions of PV processes implicitly assume that the scheduler always selects release timings. An example of this assumption is the theorem found in Habermann [1972]. In our model this theorem is a property

of PV processes and the release scheduler. Some people have stated that there are two kinds of PV. In our model there is one kind of PV process; PV processes behave differently for different schedulers.

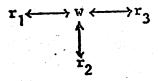

We will now use our model to state the theorem found in Habermann [1972]. Suppose that P is a PV process and that S is a semaphore. Also suppose that Q is a semi-active release timing. Define three functions as follows.

- (1)  $ns(i) = the number of k with <math>1 \le k \le i$  such that  $\alpha_k \in ready-set(\alpha_1 \cdots \alpha_{k-1})$  and  $\alpha_k$  is a V(S).

- (2)  $\operatorname{np}(i) = \operatorname{the number of } k \text{ with } 1 \le k \le i \text{ such that } \alpha_k \in \operatorname{ready-} \operatorname{set}(\alpha_1 \cdots \alpha_{k-1}) \text{ and } \alpha_k \text{ is a P(S).}$

- (3)  $nw(i) = the number of k with <math>1 \le k \le i$  such that  $\alpha_k \not\in blocked$   $set(\alpha_1 \cdots \alpha_{k-1}) \text{ and } \alpha_k \text{ is a P(S)}.$

Say the integer i performs a release iff  $\alpha_i$  is a V(S) and blockedset( $\alpha_1 \cdots \alpha_{i-1}$ ) contains a P(S). Then Habermann's theorem - in our model states that

(4) if i does not perform a release, then  $np(i) = MIN(nw(i), ns(i) + S_0)$

where S<sub>0</sub> is the initial value of S.

Habermann's theorem can be rephrased into a more intuitive form. First, n(w) - np(i) is the cardinality of the set blocked-set $(\alpha_1 \dots \alpha) \cap \{f \mid f \text{ is a P(S)}\}$ . Second,  $ns(i) + S_0 - np(i)$  is equal to  $S[value(\alpha_1 \dots \alpha_i)]$ . Thus, (4) is equivalent to

(5) if i does not perform a release, then either

(a) blocked-set(

$$\alpha_1 \cdots \alpha_i$$

) contains no P(S), or

(b)

$$S[value(\alpha_1 ... \alpha_i)] = 0$$

.

Informally, if i does not perform a release, then either there are no "blocked P(S)'s" or the "semaphore S is 0".

For example, let P = EX3 and let  $\alpha = 13523$ . The values of the functions ns, np, nw are in Table 1. Since 5 does not perform a release,

$$np(5) = MIN(nw(5), ns(5) + 1).$$

Note,  $np(4) \neq MIN(nw(4), ns(4) + 1)$ : this is true since 4 does perform a release. The relation np(i) = MIN(nw(i), ns(i) + 1) does not hold "when a release is in progress"; it does hold at all other places.

| integer i | ns(i) | np(i)  | nw(i) |

|-----------|-------|--------|-------|

| 1 1       | . 0   | 1      | 1     |

| 2         | 0     | 1      | 2     |

| 3         | 0     | 1      | 3     |

| 5         | 1     | 1<br>2 | 3     |

TABLE 1. The functions ns, np, nw for the timing 13523 in EX3

## 3.3 "FAIRNESS"

We will now define a type of timing that is related to the intuitive concept of "fairness".

6. <u>Definition</u>. Say the timing  $\alpha$  in a C process is <u>pointer-bounded</u> provided, if f is in pointer-set( $\alpha_1 \cdots \alpha_k$ ) and f is not in

pointer-set( $\alpha_1 \cdots \alpha_{k-1}$ ), then for some m > k,  $\alpha_m = f$ .

Note, if k=0, then by convention: pointer-set( $\alpha_{-1}$ ) is the empty set. Thus, if  $\alpha$  is pointer-bounded and f is in pointer-set( $\Lambda$ ), then for some m>0,  $\alpha_m=f$ .

A timing is pointer-bounded if no action "waits forever for a chance to be tried". For example, consider the timing 12... (12 repeated forever) in process EX3. This timing is active and a release timing; it is not pointer-bounded. In fact, if  $\alpha$  is a semi-active release pointer-bounded timing in EX3, then

"at least two of the subprocesses of EX3 must cycle an infinite number of times".

Caution, the timing 135231413... (231413 repeated forever) is a semiactive release pointer-bounded timing. In this timing

"one of the subprocesses of EX3 never cycles".

Thus, while the notion of pointer-bounded is a notion of "fairness", it is a weak one. Clearly, we can define schedulers that would enforce a stronger notion of "fairness".

#### 4. RELATIONS BETWEEN PROCESSES

#### 4.1 SYNCHRONIZATION PROBLEMS

One of the issues that we must face in our study of "synchronization problems" is: how are we to represent "problems"? The usual method in the synchronization area is to state a problem in some informal language. A "solution" to this kind of problem is some process and some assertions that the process satisfies. This method, however, is hard to formalize; in addition, this method cannot easily compare different solutions to the same problem.

We consider the study of synchronization problems as the study

of the relationships between processes. More exactly - in our

theory - a synchronization problem is:

- (1) a process P and.

- (2) a relation R between processes.

A solution to a synchronization problem is a process 2 such that R(2,P) is true. The components of a synchronization problem - P,R - are present in the literature definitions of synchronization problems. The process P is usually defined informally: often in English. This process defines the "behavior" that is desired. The relation R is usually defined informally. For instance, the chief source of the controversy between Brinch Hansen and Courtois, Heymans, Parnas can be attributed to their informal definitions of R. Brinch Hansen considered the second reader-writer problem to

be P, R while Courtois, Heymans, Parnas considered the second readerwriter problem to be P, R' where  $R \neq R'$ . We will say more about this controversy when we study the second reader-writer problem.

There are several advantages in our approach to problem definition.

First, any reasonable theory of processes must be interested in relations between processes. Second, we avoid introducing a new object - a "problem" - into our theory. Essentially our study of synchronization problems reduces to a study of relations between processes. This is a standard technique in many theories. For example, in finite state machine theory, relations between machines are used to define problems. Third, our approach makes clear the importance of the relation R. Many relations R are possible: we make no claim that any one relation is the only important one.

We will next present definitions of several of the relations that are implicit in the synchronization literature. We will then use our model to study the second reader-writer problem. Next we will define "simulate"; this relation is one of our central concepts. Finally, several processes will be defined; these processes define the behavior of several synchronization problems.

#### 4.2 REALIZATIONS

1. <u>Definition</u>. Suppose that 2 and P are processes. A <u>realization r</u> is a function from the timings of 2 to the timings of P such that: if  $\alpha\beta$  is a timing in  $\alpha\beta$ , then  $r(\alpha\beta) = r(\alpha)r(\beta)$ ; and for all actions  $\beta$  in  $\alpha$ ,  $\alpha$ ,  $\alpha$ ,  $\alpha$  is either A or an action in  $\beta$ .

2. <u>Definition</u>. Suppose that r is a realization from 2 to R.

Then say that the action f in 2 is <u>observable under r</u> if  $r(f) \neq \Lambda$ ;

otherwise, say that the action f is <u>unobservable under r</u>. When there can be no confusion we will drop 'under r'.

Informally, an action in 2 is unobservable provided it does a "book-keeping operation" that is not present in ?; an action is observable provided it does an "operation" that is present in ?. Note, if r is a realization from 2 to ?, then

P is an "abstraction" of 2.

Since  $\mathfrak D$  may contain unobservable actions, "detail is lost in going from  $\mathfrak D$  to  $\mathfrak P$ ".

### 4.3 SAFE REALIZATIONS

It is not obvious that the concept of realization can be used to define the relations used in the literature: "safe" and "deadlock free" (Dijkstra [1968]). We will now show that it can.

3. <u>Definition</u>. Suppose that r is a realization from D to P. Then say that r is <u>safe</u> provided

r { $\alpha$  |  $\alpha$  active in  $\Omega$ }  $\subseteq$  { $\beta$  |  $\beta$  active in P}.

Also say that r is onto safe provided

$r \{\alpha \mid \alpha \text{ active in } \mathfrak{Q}\} = \{\beta \mid \beta \text{ active in } \mathfrak{P}\}.$

Since the concept of safe is defined informally in the synchronization area, we cannot prove that our definition of safe is valid. However, we can present some evidence to show that our definition is a reasonable one. The definition of safe is equivalent to

for observable f, if f ∈ ready-sety(α), then

r (f) ∈ ready-sety(r(α)).

Informally, (1) states that whenever process 2 can "make a change", then process P can also "make a corresponding change". Clearly, this captures the concept of safe.

We are almost exclusively interested in realizations that are onto safe and not just safe. For the realization from 2 to ? that maps every timing to A is safe; it is onto safe only when ? is "trival", i.e., when A is the only active timing in ?.

## 4.4 DEADLOCK FREE REALIZATIONS

4. <u>Definition</u>. Suppose that r is a realization from 2 to ? Then say that r is deadlock free provided

if ready-set  $(\alpha)$  is empty, then ready-set  $(r(\alpha))$  is empty.

As in the case of safe, we cannot prove that our concept of deadlock free is valid. However, we can present some evidence that our definition is a reasonable one. The definition of deadlock free is

(1) if ready-set  $(\alpha)$  is empty, then ready-set  $(r(\alpha))$  is empty. Informally, this means that 2 can "halt after executing the timing  $\alpha$ " only if (P) also "halts after executing the timing  $r(\alpha)$ ". Clearly, this captures the concept of deadlock free as used in the synchronization area. Note, if the process (P) never "halts", then (1) is equivalent to

for all finite timings a, ready-set (a) is non-empty.

Also note, if the process never "halts", then any realization from to C is deadlock free.

There is an interesting connection between safe and deadlock free. Suppose that r is a realization from 2 to P. In order to avoid unnecessary complexities, suppose that for each action g in P, there is an action f in P such that r(f) = g. As we stated earlier, r is safe iff

for f observable, if  $f \in \text{ready-set}_{\mathfrak{D}}(\alpha)$ , then  $r(f) \in \text{ready-set}_{\mathfrak{D}}(r(\alpha))$ .

We can also show that r is deadlock free iff

for f observable, if ready-set  $g(\alpha)$  is empty, then  $r(f) \not\models ready-set_{\mathcal{O}}(r(\alpha))$ .

Therefore, r is deadlock free iff

(1) for f observable, if  $r(f) \in ready-set_{\mathcal{O}}(r(\alpha))$ , then  $ready-set_{\mathcal{O}}(\alpha)$  is non-empty.

The converse of safe is

(2) for observable f, if  $r(f) \in \text{ready-set}_{\mathcal{O}}(r(\alpha))$ , then  $f \in \text{ready-set}_{\mathcal{O}}(\alpha)$ .

Comparing (1) and (2), we see that <u>deadlock free is formed by weakening</u>

the converse of safe: deadlock free replaces 'f  $\in$  ready-set<sub>2</sub>( $\alpha$ )' by

'ready-set<sub>2</sub>( $\alpha$ ) is non-empty'. The converse of safe is too strong to be

of any practical value; on the other hand, deadlock free is very weak.

#### 4.5 SECOND READER-WRITER PROBLEM

We will now study the second reader-writer problem as defined by Courtois, Heymans, Parnas [1971]. In this study we will use three processes: CHP, W2, H.

(1) CHP. This is essentially the PV process used in Courtois, Heymans, Parnas [1971] to "solve" the second reader-writer problem. A formal representation of CHP is in Figure 8; an informal representation is in Figure 9. For simplicity we have assumed that there is one writer and three readers; this is done purely to avoid complexities in notation. Note, the definitions of READER-1, READER-2, READER-3 have been replaced by one general definition of READER-i (1 ≤ i ≤ 3). Also observe that action (k,i) is the k<sup>th</sup> action of READER-i; thus, (4,2) is

when  $L_2 = 4$  do  $L_2 \leftarrow 5$ ; readcount  $\leftarrow$  readcount + 1.

Finally, note that READER-1, READER-2, READER-3, and WRITER are "cyclic subprocesses"; for example, the last action of WRITER is

when  $L = 13 \text{ do } L \leftarrow 1$ ; mutex2  $\leftarrow$  mutex2 + 1

and the first action of WRITER is

when  $L = 1 \land \text{mutex2} \ge 1 \text{ do } L \leftarrow 2$ ;  $\text{mutex2} \leftarrow \text{mutex2} - 1$ .

Thus, action (13) "resets" the program counter L to 1.

```

program counter L<sub>1</sub>,L<sub>2</sub>,L<sub>3</sub>,L; (initial value 1)

integer readcount, writecount; (initial value 0)

semaphore mutex1, mutex2, mutex3, w,a; (initial value 1)

WRITER

(1) when L = 1 \land mutex2 \ge 1 do L \leftarrow 2; mutex2 \leftarrow mutex2 - 1

(2) when L = 2

do L ← 3; writecount ← writecount + 1

do L ← if writecount = 1 then 4 else 5

(3) when L = 3

do L \leftarrow 5; a \leftarrow a - 1

(4) when L = 4 \land a \ge 1

do L \leftarrow 6; mutex2 \leftarrow mutex2 + 1

(5) when L = 5

do L \leftarrow 7; b \leftarrow b - 1

(6) when L = 6 \land b \ge 1

do L ← 8

(7) \quad \text{when } L = 7

(8) when L = 8

do L \leftarrow 9; b \leftarrow b + 1

(9) when L = 9 \land \text{mutex} \ge 1 \text{ do } L \leftarrow 10; \text{mutex} 2 \leftarrow \text{mutex} 2 - 1

(10) when L = 10

do L ← 11; writecount ← writecount - 1

(11) when L = 11

do L - if writecount = 0 then 12 else 13

(12) when L = 12

do L \leftarrow 13; a \leftarrow a + 1

do L \leftarrow 1; mutex2 \leftarrow mutex2 + 1

(13) when L = 13

READER-i (1 \le i \le 3)

(1,i) when L_i = 1 \land \text{mutex3} \ge 1 \text{ do } L_i \leftarrow 2; mutex3 \leftarrow \text{mutex3} - 1

(2,i) when L_i = 2 \land a \ge 1 do L_i \leftarrow 3; a \leftarrow a - 1

(3,i) when L = 3 \land mutex1 \ge 1 do L \leftarrow 4; mutex1 \leftarrow mutex1 - 1

(4,i) \quad \underline{\text{when}} \ L_i = 4

do L, ← 5; readcount ← readcount + 1

(5,i) when L_i = 5

do L, - if readcount = 1 then 6 else 7

do L. \leftarrow 7; b \leftarrow b - 1

(6,i) when L = 6 \land b \ge 1

do L, \leftarrow 8; mutex1 \leftarrow mutex1 + 1

(7,i) when L_i = 7

do L, \leftarrow 9; a \leftarrow a + 1

(8,1) when L_{i} = 8

\underline{do} L_i \leftarrow 10; \text{ mutex3} \leftarrow \text{mutex3} + 1

(9,i) when L_i = 9

(10,i) when L_{i} = 10

do L, ← 11

(11,i) when L, = 11 \land mutex1>1 do L, \leftarrow 12; mutex1 \leftarrow mutex1 - 1

(12,i) when L_{i} = 12

do L, ← 13; readcount ← readcount - 1

(13,i) when L_i = 13

do L. \leftarrow if readcount = 0 then 14 else 15

(14,i) when L_i = 14

do L, \leftarrow 15; b \leftarrow b + 1

(15,i) when L_i = 15

do L, \leftarrow 1; mutex1 \leftarrow mutex1 + 1

```

FIGURE 8. Process CHP: formal representation

integer readcount, writecount; (initial value 0)

semaphore mutex1, mutex2, mutex3,a,b; (initial value 1)

```

WRITER

READER-i (1 \le i \le 3)

(1) P(mutex2);

(1,i)

P(mutex3);

writecount := writecount + 1;

P(a);

(2,i)

if writecount = 1 then

(3)

(3,i)

P(mutex1)

P(a);

(4)

readcount := readcount + 1;

(4,i)

(5) V(mutex2);

(5,i)

if readcount = 1 then

(6) P(b);

P(b);

(6,i)

(7) writing is performed

(7,i)

V(mutex1);

(8) V(b);

(8,i)

V(a);

(9) P(mutex2);

V(mutex3);

(9,i)

(10) writecount := writecount - 1;

reading is performed

(10,i)

(11) if writecount = 1 then

(11,i)

P(mutex1);

V(a);

readcount := readcount - 1;

(12)

(12,i)

(13) V(mutex2);

if readcount = 0 then

(13,i)

V(b);

(14, 1)

V(mutex1);

(15, i)

```

FIGURE 9. Process CHP: informal representation

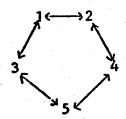

(2) W2. This is essentially the up/down process used in Wodon [1972] to "solve" the second reader-writer problem. A formal representation of W2 is in Figure 10; an informal representation is in Figure 11. As in CHP, we have assumed that there is one writer and three readers. Again observe that action (k,:) is the k<sup>th</sup> action of READER-i, thus (3,2) is

when  $L_2 = 3$  do  $L_2 \leftarrow 1$ ;  $a \leftarrow a + 1$ .

READER-1, READER-2, READER-3, and WRITER are "cyclic subprocesses" as in CHP.

```

program counter L<sub>1</sub>,L<sub>2</sub>,L<sub>3</sub>,L; (initial value 1)

semaphore a,b,s; (initial value 0)

```

#### WRITER

## READER-i $(1 \le i \le 3)$

(1,i) when

$$L_i = 1 \land s \ge 0$$

do  $L_i \leftarrow 2$ ;  $a \leftarrow a - 1$

(2,i) when

$$L_i = 2$$

do  $L_i \leftarrow 3$

(3,i) when

$$L_i = 3$$

do  $L_i \leftarrow 1$ ;  $a \leftarrow a + 1$

FIGURE 10. Process W2: formal representation

# semaphore a,b,s; (initial value 0)

```

WRITER

(1) { }: down (s);

(2) {a,b}: down (b);

(3) writing is performed

(4) { }: up (b);

(5) { }: up (s);

READER-i (1 ≤ i ≤ 3)

(1,i) {s}: down (a);

(2,i) reading is performed

(3,i) { }: up (a);

(5) { }: up (s);

[{ } is the empty set ]

```

FIGURE 11. Process W2: informal representation

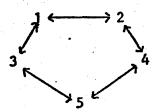

(3) H. This is essentially the PV process used in Brinch Hansen [1972a] to "solve" the second reader-writer problem. A formal representation of H is in Figure 12; an informal representation is in Figure 13. Originally, H was defined in a "structured notation"; we have expanded this notation into its PV definition. In addition, we have followed the footnote correction in Brinch Hansen [1972a]: we have inserted actions (1,i) and (11,i) (1 ≤ i ≤ 3). As in CHP and W2, we have assumed that there is one writer and three readers; also, each of these subprocesses is "cyclic".

In all three processes, we have assumed that in READER-i (1  $\leq$  i  $\leq$  3)

reading is performed

and in WRITER

writing is performed

is one action. This assumption is made purely for convenience; it does not affect our discussion. Note, we will refer to process W2 in later chapters.

As stated in Section 4.1 - in order to define the second reader-writer problem - we must supply two objects.

- (1) a process P that defines the behavior of the readers and writers,

- (2) a relation R between processes.

```

program counter L1, L2, L3, L; (initial value 1)

integer readcount, writecount, c; (initial value 0)

semaphore a,b,d,e: (initial value 1)

READER-1 (1 \leq i \leq 3)

(1,i) when L_i = 1 \land b \ge 1 \text{ do } L_i \leftarrow 2; b \leftarrow b - 1

(2,i) when L_i = 2 \land a \ge 1 \text{ do } L_i \leftarrow 3; a \leftarrow a - 1

\underline{do} L_i \leftarrow \underline{if} \text{ write count} = 0 \underline{then} 9 \underline{else} 4

(3,i) when L_i = 3

\underline{do} L_i \leftarrow 5; c \leftarrow c + 1

(4,i) \quad \underline{\text{when}} \ L_i = 4

do L_i \leftarrow 6; a \leftarrow a + 1

(5,i) \quad \underline{\text{when}} \ L_i = 5

(6,i) when L_i = 6 \land e \ge 1 \text{ do } L_i \leftarrow 7; e \leftarrow e - 1

(7,i) when L_i = 7 \land a \ge 1 \text{ do } L_i \leftarrow 8; a \leftarrow a - 1

(8,i) when L_i = 8

\underline{do} L_i \leftarrow 3

\underline{do} L<sub>i</sub> ← 10; readcount ← readcount + 1

(9,i) when L_i = 9

\underline{do} L_i \leftarrow 11; a \leftarrow a + 1

(10,i) when L_{i} = 10

(11,i) when L_i = 11

\underline{do} L_i \leftarrow 12; b \leftarrow b + 1

. \underline{do} L_i \leftarrow 13

(12,i) when L_{i} = 12

(13,i) when L_i = 13 \land a \ge 1 do L_i \leftarrow 14; a \leftarrow a - 1

do L, \leftarrow 15; readcount \leftarrow readcount - 1

(14,1) when L_{i} = 14

do L, \leftarrow if c = 0 then 19 else 16

(15,1) when L_{i} = 15

\underline{do} L_i \leftarrow 17; c \leftarrow c - 1

(16,i) when L_{i} = 16

\underline{do} L_i \leftarrow 18; e \leftarrow e + 1

(17,i) when L_i = 17

\underline{do} L_i \leftarrow 15

(18,i) when L_i = 18

\underline{do} L_i \leftarrow 1; a \leftarrow a + 1

(19,i) when L_i = 19

WRITER

do L \leftarrow 2; a \leftarrow a - 1

(1) when L = 1 \land a \ge 1

do L ← 3; writecount ← writecount + 1

(2) when L = 2

do L - if readcount = 0 then 9 else 4

(3) when L = 3

do L \leftarrow 5; c \leftarrow c + 1

(4) when L = 4

do L \leftarrow 6; a \leftarrow a + 1

(5) when L = 5

do L ← 7; e ← e - 1

(6) when L = 6 \land e \ge 1

do L \leftarrow 8; a \leftarrow a - 1

(7) when L = 7 \land a \ge 1

do L ← 3

(8) when L = 8

do L \leftarrow 10; a \leftarrow a + 1

when L = 9

```